# Lecture Notes in Computer Science 3432

Commenced Publication in 1973

Founding and Former Series Editors:

Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

#### **Editorial Board**

**David Hutchison**

Lancaster University, UK

Takeo Kanade

Carnegie Mellon University, Pittsburgh, PA, USA

Josef Kittler

University of Surrey, Guildford, UK

Jon M. Kleinberg

Cornell University, Ithaca, NY, USA

Friedemann Mattern

ETH Zurich, Switzerland

John C. Mitchell

Stanford University, CA, USA

Moni Naor

Weizmann Institute of Science, Rehovot, Israel

Oscar Nierstrasz

University of Bern, Switzerland

C. Pandu Rangan

Indian Institute of Technology, Madras, India

Bernhard Steffen

University of Dortmund, Germany

Madhu Sudan

Massachusetts Institute of Technology, MA, USA

Demetri Terzopoulos

New York University, NY, USA

Doug Tygar

University of California, Berkeley, CA, USA

Moshe Y. Vardi

Rice University, Houston, TX, USA

Gerhard Weikum

Max-Planck Institute of Computer Science, Saarbruecken, Germany

# Michael Beigl Paul Lukowicz (Eds.)

# Systems Aspects in Organic and Pervasive Computing – ARCS 2005

18th International Conference on Architecture of Computing Systems Innsbruck, Austria, March 14-17, 2005 Proceedings

#### Volume Editors

Michael Beigl University of Karlsruhe Telecooperation Office (TecO) Vincenz-Priessnitz-Strasse 1 76131 Karlsruhe, Germany E-mail: michael@teco.edu

Paul Lukowicz

University for Health Science, Medical Informatics and Technology

Innsbruck, Austria

E-mail: paul.lukowicz@umit.at

Library of Congress Control Number: 2005921801

CR Subject Classification (1998): C.2, C.5.3, D.4, D.2.11, H.3.5, H.4, H.5.2

ISSN 0302-9743 ISBN 3-540-25273-8 Springer Berlin Heidelberg New York

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer. Violations are liable to prosecution under the German Copyright Law.

Springer is a part of Springer Science+Business Media

springeronline.com

© Springer-Verlag Berlin Heidelberg 2005 Printed in Germany

Typesetting: Camera-ready by author, data conversion by Olgun Computergrafik Printed on acid-free paper SPIN: 11398196 06/3142 5 4 3 2 1 0

### **Preface**

The key challenge for future computer system is dealing with complexity. On one hand this involves internal system complexity which has increased exponentially over recent years. Here the main objectives are to maintain system reliability and to keep the design and maintenance effort manageable, while at the same time continuing to provide new functionality and increasing system performance. This has been the focus of so-called autonomous computing, which aims to bring self-configuration and repair to a wide range of computing systems.

On the other hand future computer systems are more and more becoming integrated into the fabric of everyday life and thus have to deal with the complexities of the real world. They will become smaller, more appropriate for their use, integrated into everyday objects, and often virtually or physically invisible to the users. They will also be deployed in a much higher quantity and penetrate many more application areas than traditional notions of computer systems. This requires computer systems to be adaptable within a much wider range of possible tasks, subjected to much harsher conditions.

To provide such features and functionality, computer devices will become tinier yet still increase in system complexity; they must consume less power, while still supporting advanced computation and communications, such that they are highly connected yet still operate as autonomous units. Pervasive and ubiquitous computing research addresses such issues by developing concepts and technology for interweaving computers into our everyday life. The principal approach is to enhance system functionality and adaptability by recognizing context and situations in the environment.

Organic computing deals with high system complexity by drawing analogies from complex biological systems, with the human-centered goal of self-organization. It addresses both internal system complexity of conventional systems and the complexity involved in pervasive environments dealing with the real world. Thus organic computing investigates the design and implementation of self-managing systems that are self-configuring, self-optimizing, self-healing, self-protecting, context aware, and anticipatory. It touches upon a number of exciting research topics including ultra-low power consumption, scalability and complexity of devices and systems, self-awareness, adaptive networking, and smart behavior of systems.

Many papers submitted to the Architecture of Computing Systems Conference (ARCS) address these aspects of adaptable, self-organizing systems. For computer system hardware, reconfigurable hardware allows us to optimize the system performance based on the application context, relieving software developers from detailed consideration of the inherently inflexible hardware constraints. Adaptive methods for managing resources and tasks enable (embedded) microprocessor systems to be both real-time aware but also very low in their power consumption. In software, middleware agents are able to cope with changes in

application and environment, thus still providing a minimum of functionality even under difficult and changing conditions.

Adaptive ad hoc communication networks and context-aware pervasive systems and applications provide the functionality mostly visible to the end user of such systems. To achieve this extent of adaptivity a large variety of methods were used – many of them borrowed from nature. The papers in this book present a good profile of such novel methods and their application in the area of computing systems.

This year the ARCS conference selected 18 papers from a competitive field of 52 submissions from 12 countries. All papers accepted for presentation were peer reviewed and discussed in the first step in an online discussion among members of the international Program Committee. In the PC Meeting then the final decisions were made based on these reviews and the online discussions. Care was taken to avoid any conflict of interest by handing out papers and discussion papers only to PC members not involved in or related to the work.

We would like to take the opportunity to thank the numerous people who supported us in organizing the paper program and the conference: the Program Committee members for their efforts in reviewing many papers; Uwe Brinkschulte for supporting us by serving as the Workshops and Tutorials Chair; and the General and Program Chairs, Christian Müller-Schloer and Theo Ungerer, for sharing their experience with us and helping us to organize the paper program and the conference.

We extend our gratitude to several organizations that provided financial and organizational support for the ARCS conference. Volker Schanz from the ITG provided the legal framework and the ARCS Fachausschuss, the organizational body of the conference. Financial and organizational support came from the APS+PC group, which organized and funded a special session with several interesting invited talks. Donations also came from our benefactor, Siemens AG. We would also like to thank Christian Decker and Michael Biebl for their help during the electronic submission process, and the University for Health Sciences, Medical Information and Technology in Innsbruck, Austria for hosting the conference.

January 2005

Michael Beigl Program Chair ARCS 2005

Paul Lukowicz General Chair ARCS 2005

#### Executive Committee

Conference Chair: Paul Lukowicz University for Health Sciences, Medical

Informatics and Technology, Austria

Program Chair: Michael Beigl University of Karlsruhe, Germany

Workshops and

Tutorials Chair: Uwe Brinkschulte University of Karlsruhe, Germany

# **Program Committee**

Shigeru Ando University of Tokyo, Japan

Nader Bagherzadeh

Frank Bellosa

University of California, Irvine, USA

University of Erlangen, Germany

University of Karlsruhe, Germany

Roy Campbell University of Illinois at Urbana-Champaign, USA

Alois Ferscha University of Linz, Austria

Paul Havinga University of Twente, Netherlands Wolfgang Karl University of Karlsruhe, Germany

Jürgen Kleinöder Universität Erlangen-Nürnberg, Germany

Rudolf Kober Siemens AG, München, Germany

Spyros Lalis University of Thessaly, Greece

Erik Maehle Universität zu Lübeck, Germany

Christian Müller-Schloer

Joe Paradiso MIT Media Laboratory, USA

Burghardt Schallenberger Siemens AG, Germany

Hartmut Schmeck University of Karlsruhe, Germany

Albrecht Schmidt LMU Munich, Germany

Karsten Schwan Georgia Institute of Technology, USA Rainer G. Spallek Technische Universität Dresden, Germany

Peter Steenkiste Carnegie Mellon University, USA Yoshito Tobe Tokyo Denki University, Japan

Hide Tokuda Keio University, Japan

Theo Ungerer University of Augsburg, Germany

Klaus Waldschmidt University of Frankfurt, Germany

Lars Wolf University of Braunschweig, Germany

Martina Zitterbart University of Karlsruhe, Germany

# Organization

The Architecture of Computing Systems (ARCS) Conference was organized by the ITG (Informationstechnische Gesellschaft – Information Technology Society) and the Special Interest Group on Computer and Systems Architecture of the GI (Gesellschaft für Informatik – German Informatics Society), supported by OCG (Austrian Computer Society), OVE/GIT (Austrian Electrotechnical Association) and electrosuisse (ITG), and held in cooperation with ACM.

# **Sponsor**

Siemens AG, Munich, Germany

# Table of Contents

| Adaptation, Power Consumption and Scheduling                                                                                                            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| Energy Management for Embedded Multithreaded Processors with Integrated EDF Scheduling                                                                  |

| Reducing System Level Power Consumption<br>for Mobile and Embedded Platforms                                                                            |

| Implementing Control Algorithms Within a Multithreaded Java Microcontroller                                                                             |

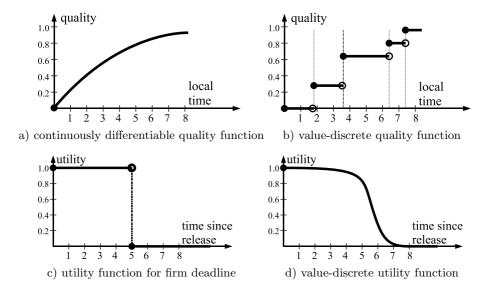

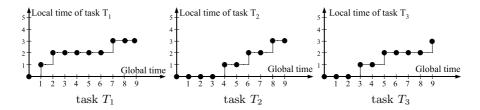

| Adaptivity for Quality and Timeliness Flexible Real-Time Systems                                                                                        |

| Adaptation and Agents                                                                                                                                   |

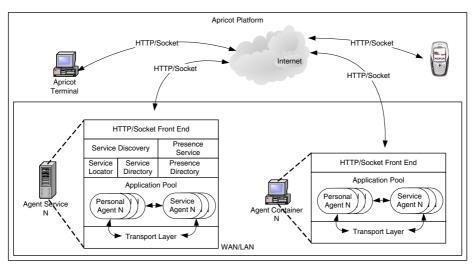

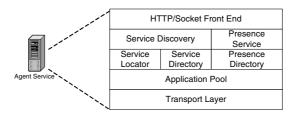

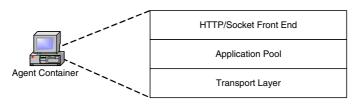

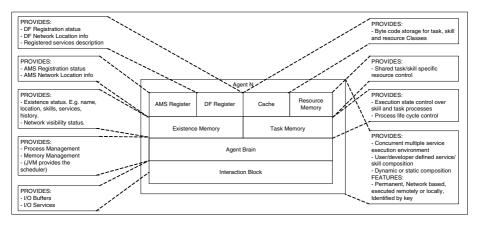

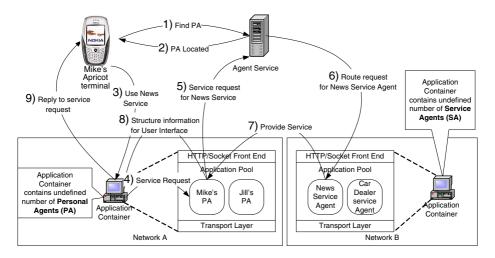

| Apricot Agent Platform for User-Friendly Mobile Service Development 65  Petteri Alahuhta, Henri Löthman, Heli Helaakoski, Arto Koskela, and Juha Röning |

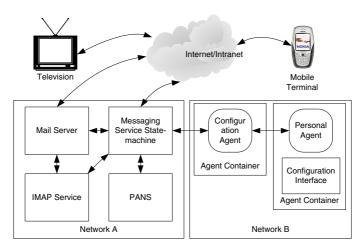

| Support of Reflective Mobile Agents in a Smart Office Environment                                                                                       |

| Learning Action Sequences Through Imitation in Behavior Based Architectures                                                                             |

| Adaptation and Services                                                                                                                                 |

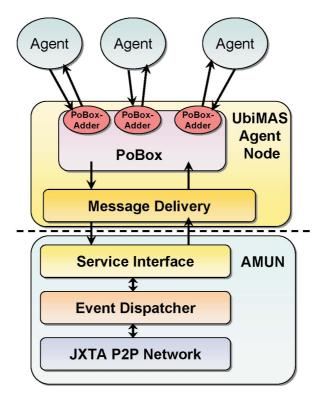

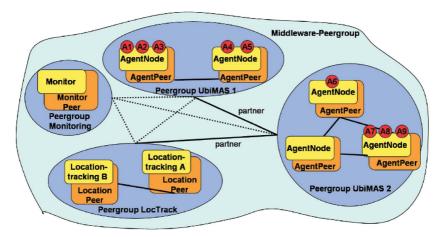

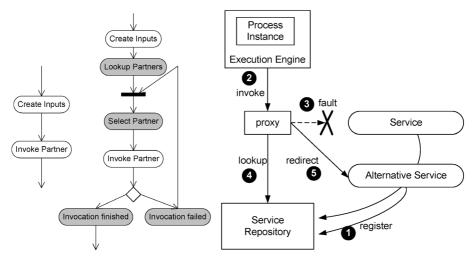

| Self-healing Execution of Business Processes  Based on a Peer-to-Peer Service Architecture                                                              |

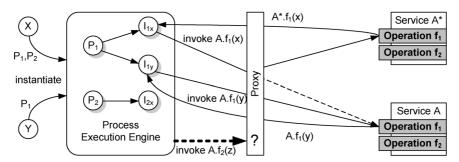

| Runtime Adaptation of Applications Through Dynamic Recomposition of Components                                                                          |

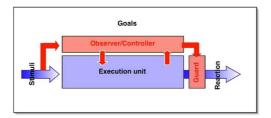

| An Observer/Controller Architecture for Adaptive Reconfigurable Stacks 139 Thorsten Schöler and Christian Müller-Schloer                                |

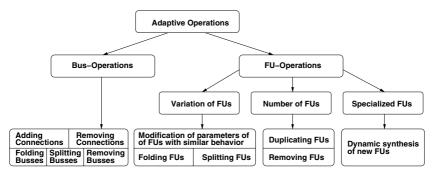

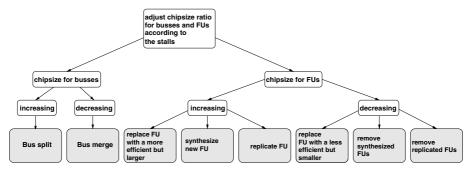

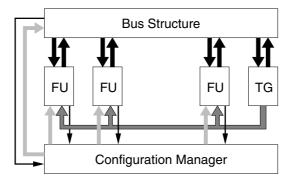

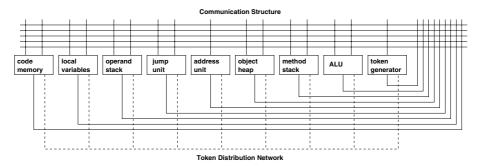

| The Organic Features of the AMIDAR Class of Processors                                                                |

|-----------------------------------------------------------------------------------------------------------------------|

| Reusable Design of Inter-chip Communication Interfaces for Next Generation of Adaptive Computing Systems              |

| DESCOMP: A New Design Space Exploration Approach                                                                      |

| Design Space Navigation for Neighboring Power-Performance Efficient Microprocessor Configurations                     |

| An Efficient Frequency Scaling Approach for Energy-Aware Embedded Real-Time Systems                                   |

| Pervasive Computing and Communication                                                                                 |

| Towards Autonomic Networking Using Overlay Routing Techniques 222<br>Kendy Kutzner, Kurt Cramer, and Thomas Fuhrmann  |

| Context-Based Storage Management for Wearable and Portable Devices $$ 236 $$ Alexandros Karypidis and Spyros Lalis    |

| A File System for System Programming in Ubiquitous Computing 249<br>Christian Decker, Michael Beigl, and Albert Krohn |

| Author Index                                                                                                          |

# Energy Management for Embedded Multithreaded Processors with Integrated EDF Scheduling

Sascha Uhrig and Theo Ungerer

Institute of Computer Science, University of Augsburg, 86159 Augsburg, Germany

Tel.: +498215982353, Fax.: +498215982359

{uhrig,ungerer}@informatik.uni-augsburg.de

**Abstract.** This paper proposes a new hardware-based energy management technique for future embedded multithreaded processors with integrated Earliest Deadline First (EDF) real-time scheduling. Our energy management technique controls frequency reduction and dynamic voltage scaling depending on the deadlines, the Worst Case Execution Times (WCET), and the real execution times. Hard real-time capability can be guaranteed for aperiodic threads and for threads with deadlines shorter than their period. Our evaluations show that energy consumption can be reduced up to about  $\frac{2}{3}$  of a comparable software-based algorithm.

**Keywords:** energy management, energy-aware program execution, realtime scheduling, multithreading, EDF scheduling

#### 1 Introduction

The reduction of energy consumption is an important research field because of the rapidly growing number of battery-powered mobile and embedded devices. Hard real-time is often an essential requirement for such systems. This paper focuses on energy management in embedded processor cores in combination with real-time applications. The aim is to reduce the total energy consumption by optimizing power consumption without delaying the completion of the real-time threads.

In CMOS devices, the power consumption is proportional to the square of the supply voltage and linear to the frequency:

$$P_{cmos} = aC_L V_{DD}^2 f,$$

where a is the activity of the circuit,  $C_L$  is the output load capacity,  $V_{DD}$  the supply voltage, and f the frequency. Obviously, power consumption can be reduced dynamically by decrementing supply voltage and clock frequency. Unfortunately, supply voltage depends on clock frequency and, using lower frequency, the processor's performance is reduced too. Hence, in real-time systems, we have to control frequency in a way which does not harm the real-time behavior of the system.

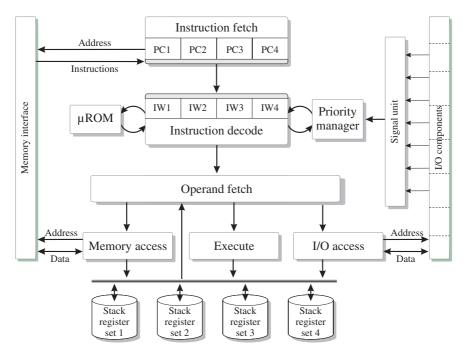

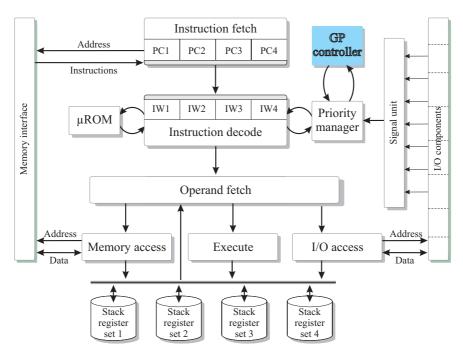

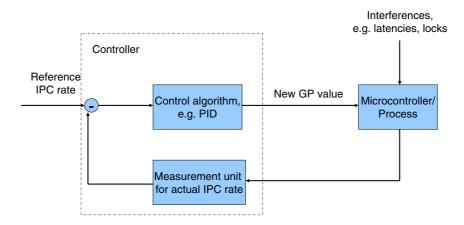

We developed a multithreaded Java microcontroller – called Komodo microcontroller – with hardware-integrated real-time scheduling schemes [1, 2] for application in embedded real-time systems and ubiquitous devices. The Komodo microcontroller is able to perform a thread switch without any overhead. Thus, instructions of active threads are executed in an overlapped fashion inside the core pipeline; the EDF scheduler hardware ensures that the thread with the earliest deadline is the thread with the highest priority. Due to hardware multithreading, instructions of other threads are executed within latency cycles of the thread with the highest priority without interfering with its execution (latency bridging).

We investigate mechanisms to minimize energy consumption using hardware-based energy management techniques that are made possible by a multithreaded processor core with integrated EDF scheduling. In particular, we show that energy saving techniques like frequency reduction and voltage scaling can be controlled more efficient by the integrated EDF energy management than using conventional operating system methods. Our hardware-integrated energy management algorithm chooses automatically in each processor cycle the frequency and voltage level that is currently required to perform a real-time application without any miss of deadline.

The next two sections show state-of-the-art energy saving mechanisms and related work. Section 4 presents the extensions for hardware-based energy management within the processor-integrated EDF scheduler and in section 5 we evaluate our approach. Section 6 concludes the paper.

# 2 State-of-the-Art Energy Saving Mechanisms

Commercial processors use a number of techniques for saving energy like pipeline gating, several suspend or sleep modes, and reduction of frequency and supply voltage. Intel's XScale [3], Transmeta's Crusoe [4] and the MSP430 [5] from Texas Instruments work with software-controlled techniques of frequency reduction and voltage scaling.

We describe shortly the energy saving features of the XScale and the Crusoe processors, because we use their electrical properties (voltages and frequency rates) for simulating our hardware-based energy management. Both processors are able to run at several frequencies using different supply voltages. A change of frequency requires among other tasks to complete all outstanding memory accesses, to set the external SDRAM to self-refresh mode, and to disable the interrupt controller. Most tasks are done automatically, but, nevertheless, they need time for execution. The whole process of changing frequency requires up to  $500\mu s$  in the case of the XScale. Using the Crusoe processor, the time required for a supply voltage change depends on the distance of the two voltage levels. The maximum value is about  $896\mu s$  in the default configuration.

Pipeline Gating [6] is a technique for selectively disconnecting parts of the processor, especially pipeline stages. So the energy consumption can be reduced by uncoupling unnecessary parts of the pipeline without concerning any other component. In contrast, frequency and voltage scaling affect the whole circuit.

# 3 Related Work on Real-Time Energy Management

Different directions of research targeting real-time applications are present: energy management controlled by the application, the operating system, or by the hardware itself. Application-based power management requires special power control sequences within the application's program code. Shin et al. [7] present a technique for automatic insertion of power controlling code based on a WCET analysis before runtime. The suggested mechanism is feasible for hard real-time systems.

In contrast to application-based techniques, other approaches focus on frequency and voltage reduction controlled by the operating system, especially by its thread scheduler. Pillai et al. [8] present several energy-aware scheduling schemes similar to the EDF scheduling scheme for low-power embedded real-time operating systems. Jejurikar et al. [9] focus on the problem of task synchronization in combination with energy-aware task scheduling. Pouwelse et al. [10, 11] describe a hybrid approach, which is based on an extended Linux OS with a so-called energy priority scheduling. The parameters for the scheduler are given by the application.

A theoretical approach for an energy saving technique using EDF scheduling is presented by Krishna et al. [12, 13]. Their energy management is based on an offline thread schedule, the online schedule, an offline and an online function, which describe the amount of work to do. Aydin et al. [14] additionally use a speculative speed adjustment for periodic real-time tasks.

All presented techniques are based on a single-threaded processor core and a software-based energy management. Energy management investigations concerning multithreaded processors pertain simultaneous multithreading and are made by [15, 16]. Energy management of a multithreaded single-issue processor with integrated Guaranteed Percentage (GP) hardware real-time scheduling was evaluated by ourselves [17, 18].

All existing processors and research approaches (except our GP energy management) suffer from the inefficiency of software control: Calculating the optimal frequency and the supply voltage by software requires a software overhead. Additionally, most control techniques assume a continuous frequency control which is not realistic. In real processors, frequency is selected by binary clock multipliers and dividers, i.e. only discrete frequency levels are possible. A more efficient solution is a hardware-based energy management, i.e. the processor core decides to run at the optimal frequency and voltage level by itself and is able to readjust frequency and voltage during thread execution.

Another drawback of existing energy management techniques in combination with real-time scheduling is the often used assumption, that the deadline of each thread has to be equal to its period. Krishna et al. and Aydin et al. additionally require an offline thread "execution" for determining the *amount of work* function and the offline schedule itself for the energy management.

### 4 Hardware-Based Energy Management Mechanism

#### 4.1 Thread Model

For our energy management technique we permit arbitrary activation of threads with the constraints that all threads are independent and that a thread will only be restarted after its completion, i.e. at most one instance of each thread is active at a time. In the case of periodic threads, we do not make the assumption that their deadlines are equal to their periods.

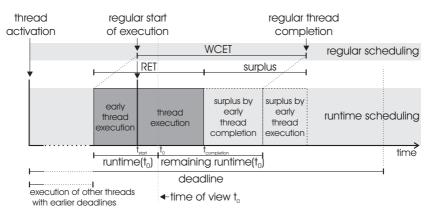

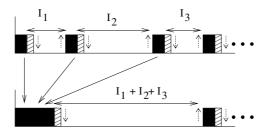

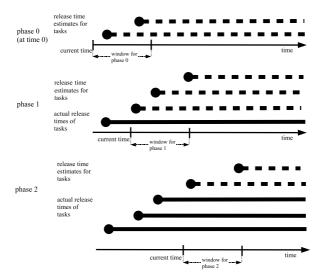

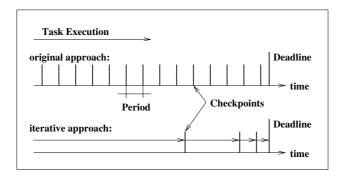

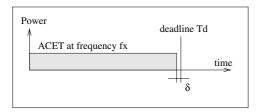

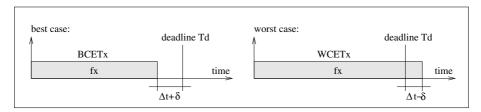

For the realization of our proposed energy management technique, several characteristics of the execution of a thread are necessary. Fig. 1 illustrates the required values which are measured in execution cycles. The figure is divided into two scheduling areas: the upper area describes the regular thread scheduling which is similar to Krishna's offline scheduling, with the difference that it is generated online by the knowledge of the WCETs and the deadlines of the already completed and all actually active threads. The lower area mirrors the scheduling depending on the real runtime behavior of the threads, i.e. the runtime scheduling. In addition to these two schedulers a third scheduler, not shown in the figure, called execution scheduler is present. It is responsible for the selection of the thread executed within the multithreaded processor pipeline in the current clock cycle. Because of the latency bridging, the scheduling decision temporarily alternates between different threads.

Fig. 1. Characteristics during the execution of a thread.

The deadline and the WCET are given by the application and stored as constants within the energy management unit. The surplus are the remaining cycles from thread completion to the regular (planned) completion of the thread assuming that all previous threads have exhausted their WCET too. The  $runtime(t_0)$  represents the amount of execution cycles the current thread has executed up to time  $t_0$ . In general, due to the multithreaded execution and the surplus of the previous thread, an  $early\ thread\ execution\ takes\ place\ and\ thus, the <math>runtime(t_{start})$

is greater than zero at the regular start of execution. At thread completion, the  $runtime(t_{completion})$  is equal to the real execution time (RET). The remaining  $runtime(t_0)$  is the number of cycles the thread will run from time  $t_0$  (assuming its WCET), i.e., the difference between the WCET and the  $runtime(t_0)$ . The surplus is the sum of the surplus by early thread completion and the surplus by early thread execution (surplus of the previous thread).

#### 4.2 Methodology

The idea behind the hardware-based energy management mechanism is that the active threads rarely need the time calculated as WCET for the actual execution as it is reported in [19]. Thus frequency can be reduced such that all threads terminate as late as possible but not later than the time predicted by the schedulability analysis (depending on the WCETs). As a consequence, the supply voltage can be adapted to a level corresponding to the throttled frequency, which may lead to a tremendous energy saving. Because of the direct relationship between the selected clock frequency and the required supply voltage, determining the optimal clock frequency is the real challenge.

Using a software-based solution, frequency and voltage selection is only possible at the time of a thread suspend or activation (intertask DVS) or at dedicated points during thread execution (intratask DVS). In contrast to a software-based version, our hardware-based energy management is able to observe the progression (in execution cycles) of all active threads continuously. Thus, clock frequency and supply voltage can be adapted dynamically during the thread's execution to approximate the optimal execution speed.

At the time of a thread suspend the presented energy saving mechanism registers the number of execution cycles remaining to the regular thread suspend, i.e. the surplus. Due to the surplus of the just suspended thread the execution of the thread directly following can be slowed down. The optimal frequency  $f_{reduced}$  can be calculated by the formula

$$f_{reduced} = \frac{WCET}{surplus + WCET} * f_{max},$$

where  $f_{max}$  is the maximum frequency of the processor, WCET is the WCET of the new thread, and surplus is the surplus of the just suspended thread. If the processor is working at the calculated optimal frequency  $f_{reduced}$  and the new thread requires its complete WCET, its execution completes exactly at the time planned by the schedulability analysis. If the new thread does not need its WCET for execution it offers a surplus to the following thread. Usually only fixed frequency levels are provided by the processor. So the optimal frequency cannot be selected and a frequency higher than the optimal one has to be chosen. As result, the really required energy is higher than the theoretical necessary energy.

#### 4.3 Implementation

To realize the EDF energy management the following set of five hardware registers are required for each hardware thread slot:

- $WCET_{reload}$ : This register is addressable by the software. It contains the reload value of the WCET.

- $WCET_{surplus}$ : The  $WCET_{surplus}$  register is an internal register within the energy management unit. At every thread activation it will be automatically reloaded with the value stored in the  $WCET_{reload}$  register. During runtime it will be decreased according to the algorithm described below.

- $WCET_{remain}$ : This register is very similar to the  $WCET_{surplus}$  register. The difference between these two registers is the way of decrease also described below.

- $DL_{reload}$ : The  $DL_{reload}$  register holds the deadline of the corresponding thread. It is software addressable.

- $DL_{count}$ : At the time of a thread activation, this register will be initialized with the value of the  $DL_{reload}$  register. It is decremented in every clock cycle and is responsible for the thread scheduling. Both deadline registers are required for the thread scheduling and are already available within the priority manager.

Depending on the thread scheduling, selective registers are updated in every execution cycle by hardware. Both *reload* registers have to be set by the application with the help of special instructions.

Register Actualization: The  $WCET_{surplus}$  and the  $WCET_{remain}$  registers have to be updated corresponding to the actual thread execution. That means, the  $WCET_{remain}$  register of a thread is decremented iff an instruction of this thread is executed in the actual execution cycle, i.e. it reflects the execution cycles remaining until the maximum thread execution cycles. Whereas the  $WCET_{surplus}$  register has to be reduced iff the corresponding thread is currently the regular thread, i.e. assuming the WCET of all previously executed threads. At the time of thread suspend, the  $WCET_{surplus}$  register mirrors the surplus which is available for the execution of other threads.

The scheduling decision of the regular scheduler depends only on the deadlines and the WCETs of all active threads. The execution scheduling evaluates additionally the fill level of the instruction windows, possible latencies, and the real completion of the threads.

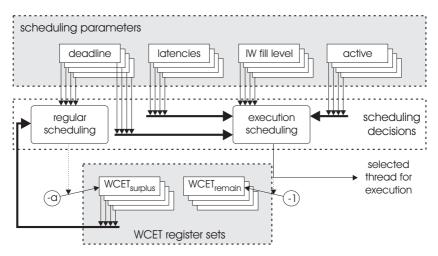

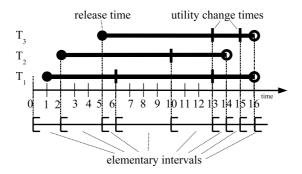

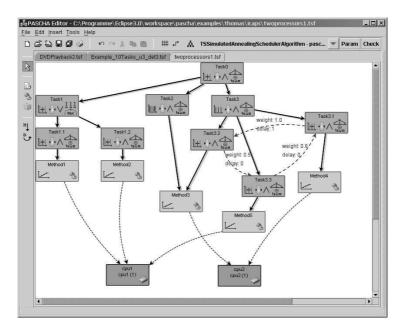

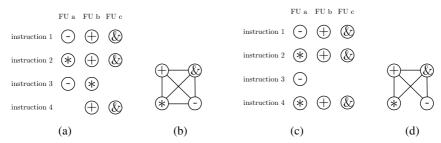

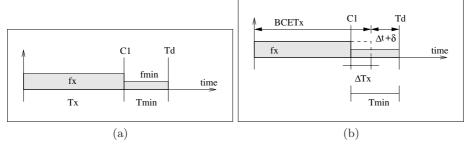

Fig. 2 demonstrates the correlation of the scheduling parameters, the scheduling decisions, and the decrease of the WCET registers. The scheduling parameters deadline, latencies, IW (instruction window) fill level, and the active flags are required for the execution scheduling. The WCET register sets are only required for the energy management. The  $WCET_{surplus}$  and the  $WCET_{remain}$  registers are updated depending on the regular respectively the execution scheduling. A set of all registers is available for each hardware thread slot.

**Frequency and Voltage Control:** For frequency and voltage control an additional third scheduler, the *runtime scheduler* is required, which is not shown in figure 2. Its task is to determine the thread with the highest priority in execution. In contrast to the *execution scheduler*, the *runtime scheduler* ignores the fill levels

Fig. 2. Decrease of the WCET registers in correlation with the scheduling. The decrease value a depends on the selected execution frequency.

of the instruction windows and occurring latencies. Thus, the *runtime scheduler* designates the current active thread with the highest priority disregarding its feasibility.

For the selection of the execution frequency, the energy management unit has to distinguish between three cases:

- 1. The decision of the *runtime scheduler* is invalid. In this case, no active thread is available. Frequency and supply voltage can be reduced to the minimum level.

- 2. The decisions of the runtime scheduler and the regular scheduler are identical. The maximum number of cycles the thread will be executed is known within the register  $WCET_{remain}$  and the number of cycles available till the regular completion of the thread is stored in register  $WCET_{surplus}$ . The execution frequency can be reduced or has to be increased to

$$f_{reduced} = \frac{WCET_{remain}}{WCET_{surplus}} \times f_{max}.$$

3. As last case, the regular thread is not the same as the thread determined by the *runtime scheduler*. This means, a previous thread completes before its WCET and its surplus is available for the execution of the thread selected by the *runtime scheduler*. The execution frequency has to be set to:

$$f_{reduced} = \frac{WCET_{remain\_runtime}}{WCET_{surplus\_regular} + WCET_{surplus\_runtime}} \times f_{max},$$

where  $WCET_{remain\_runtime}$  and  $WCET_{remain\_runtime}$  are the corresponding registers of the thread determined by the *runtime scheduler* and  $WCET_{surplus\_regular}$  is the  $WCET_{surplus}$  register of the regular thread.

We assume that the clock generator works with a clock divider without any settling time. In our simulations we used the following divisors: 1, 1.5, 2, 2.5, 3, 3.5, 4, 4.5, 5, 10, and 14. How we determine the optimal execution frequency is now shown at the example of case 3 (see above). The following formula must be fulfilled by the minimal possible frequency:

$$f_{reduced} \geq \frac{WCET_{remain\_runtime}}{WCET_{surplus\_regular} + WCET_{surplus\_runtime}} \times f_{max}.$$

$f_{reduced}$  is derived from  $f_{max}$  by a clock divider.  $Div_{num}$  is the numerator and  $Div_{denom}$  the denominator of the clock divider:

$$f_{reduced} = f_{max} / \frac{Div_{num}}{Div_{denom}}.$$

Combining both formulas leads to the following inequation:

$$f_{max} / \frac{Div_{num}}{Div_{denom}} \ge \frac{WCET_{remain\_runtime}}{WCET_{surplus\_regular} + WCET_{surplus\_runtime}} \times f_{max}$$

$$\Leftrightarrow$$

$$Div_{denom} \times (WCET_{surplus\_regular} + WCET_{surplus\_runtime})$$

$$\ge Div_{num} \times WCET_{remain\_runtime}$$

Using the mentioned clock divider, all multiplications can be mapped to shift operations and at maximum one addition. In parallel to the frequency selection, supply voltage is chosen using a lookup table and the calculated frequency divider as index. In contrast to the voltage which is set immediately, frequency is set after a delay iff an increased voltage is required (see 4.5). In between, the processor continues working at the lower frequency.

#### 4.4 Readjusting Frequency

In most cases, the selection of the optimal frequency is not possible. Therefore, the energy management technique has to choose a frequency higher than the optimal one because otherwise the actual executed thread could terminate after the regular termination. While the thread is executed at the higher frequency than the optimal one, the progression is also higher than required.

At the time the thread's progress reaches a level such that frequency can be decreased below the optimal one, the energy management slows down the processor to this frequency. Additionally, supply voltage could be decreased. The dynamic readjustment of frequency and voltage at any time during thread execution can only be afforded by a hardware-based solution which monitors the thread's progression consistently.

#### 4.5 Impact on WCET

Using the policy described in section 4.4, an increase of the execution frequency may be necessary. In this case, the supply voltage has to be adapted first (because

of the capacity of the circuit) before the execution frequency can be increased. We called this delay the *frequency increase delay* which is the only impact of the energy management to the timing behavior of the system. The WCET of each thread has to be increased by the *frequency increase delay*. The necessity of this delay can be demonstrated by the following situation: The processor is running at a low frequency and a low supply voltage. Now, a new thread with the highest priority is activated. Because of the unknown runtime behavior of the new thread, the processor has to run at the highest frequency and voltage. Thus, first voltage has to be increased and just after voltage reached the required level, i.e. after the *frequency increased delay*, frequency can be increase too.

Another case, in which the frequency increase delay is important is the simultaneous change of the regular thread and the thread with the highest priority. Hence, due to the unknown runtime behavior of the second thread, the processor has to run at highest frequency. To allow running at high frequency immediately, supply voltage has to be set to the highest level before the first thread completes regularly, i.e. when the  $WCET_{surplus}$  register of the first thread is less than the frequency increase delay.

#### 4.6 Drawback During Switching

Within all software energy-management techniques known to us, voltage and frequency switching is done in one iteration. Hence, this step takes at least as long as the voltage needs to reach the required level (assuming a voltage increase) and no useful work can be done in the meanwhile. Our hardware-based energy-management controls frequency and voltage in two steps without halting the processor. It still runs at the lower frequency until the voltage reaches the upper level. The time, the processor runs at the lower level is taken into account at the selection of the target frequency and voltage. Therefore, a high number of voltage and frequency changes is rather an advantage than a disadvantage.

#### 5 Evaluation

#### 5.1 Processor Models

As proof of our concept we built the described energy management technique into the VHDL model of the multithreaded, single-issue Komodo processor core with integrated EDF scheduling [2, 20]. Besides the energy management itself, we integrated a clock divider with 11 different output frequencies. To avoid the assumption of  $f \sim U$ , we used the more realistic voltage levels derived from the Crusoe respectively the XScale processor and the appropriate clock dividers shown in table 1.

All benchmarks are performed by simulating the VHDL model. The frequency divider supports the clock dividers shown in table 1. Each benchmark is simulated twice: first using the voltage levels similar to the Crusoe technology (Crusoe-style), second using the voltage levels corresponding to the XScale technology (XScale-style). In addition to these two technologies we used three different energy management techniques per benchmark:

|         | -        |          |         |          |          |

|---------|----------|----------|---------|----------|----------|

| Clock   | XScale's | Crusoe's | Clock   | XScale's | Crusoe's |

| divider | voltage  | voltage  | divider | voltage  | voltage  |

|         | [V]      | [V]      |         | [V]      | [V]      |

| 1       | 1.1      | 1.3      | 4       | 0.85     | 0.8      |

| 1.5     | 1.0      | 1.05     | 4.5     | 0.85     | 0.8      |

| 2       | 1.0      | 0.95     | 5       | 0.85     | 0.8      |

| 2.5     | 1.0      | 0.875    | 10      | 0.85     | 0.8      |

| 3       | 0.85     | 0.85     | 15      | 0.85     | 0.8      |

| 3.5     | 0.85     | 0.8      |         |          |          |

**Table 1.** Voltage levels assumed for the simulation derived from the XScale and the Crusoe processor's supply voltage levels.

- 1. Assuming a single threaded microcontroller with pipeline gating requiring in gated mode 40% of the total energy consumption.

- 2. Assuming a single threaded microcontroller and a software-based EDF energy management similar to that presented by Pillai et al. [8].

- 3. The multithreaded microcontroller with integrated energy management. We assumed an overhead of 8% energy consumption for the additional hardware effort. This value is derived from the additional hardware cost for energy management.

Energy consumption is estimated by tracking the core frequency in combination with the selected voltage level and the formula of section 1. Because energy is proportional to the clock frequency we just calculate the relative energy consumption.

#### 5.2 Benchmarks

We performed two synthetic benchmarks and a realistic benchmark for evaluating the behavior of the hardware-based EDF energy management.

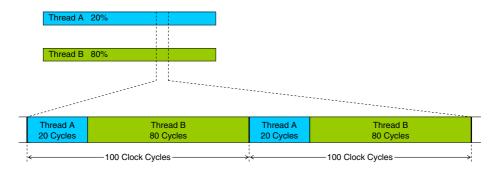

**Synthetic Benchmarks:** Each synthetic benchmark consists of four threads with a growing processor utilization. The WCETs and the periods of all threads are chosen in the way that the theoretical processor load of a whole benchmark is 100%. During the execution of both benchmarks, the real processor utilization is growing from nearly 0% at the beginning to finally 100% of computing power.

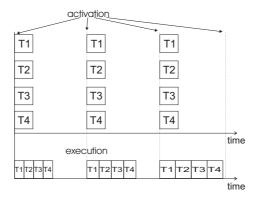

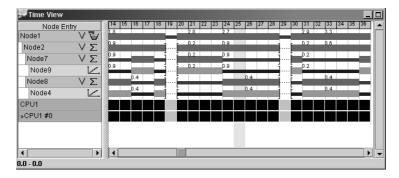

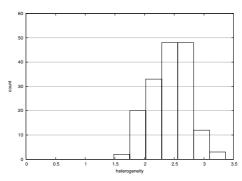

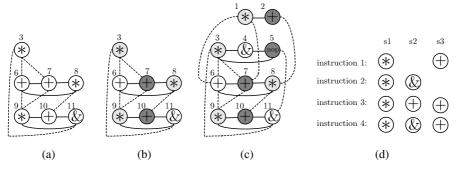

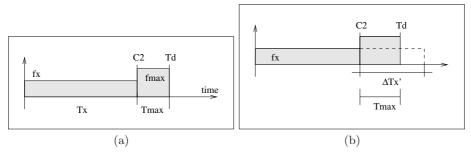

Within the first benchmark (EQUAL) all four threads were activated simultaneously with identical periods. Figure 3 illustrates the activation and the growing real computing time of the threads. In contrast, the threads within the second benchmark (DIFF) were activated at different times using different periods (see table 2).

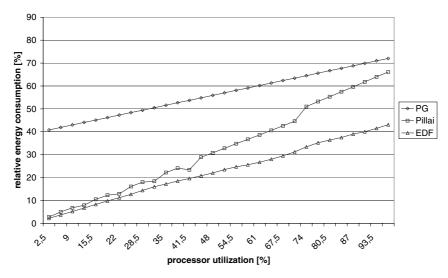

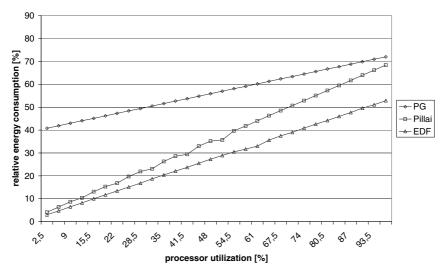

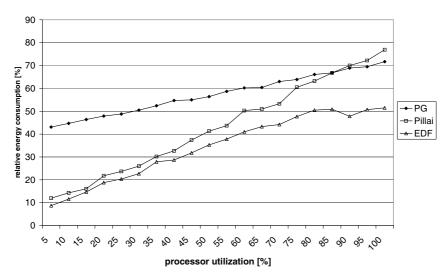

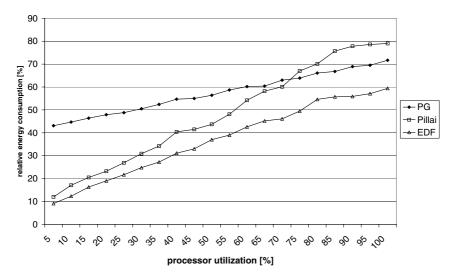

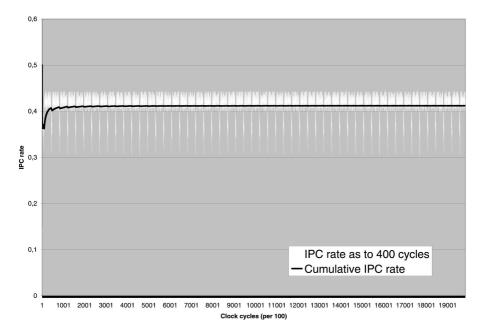

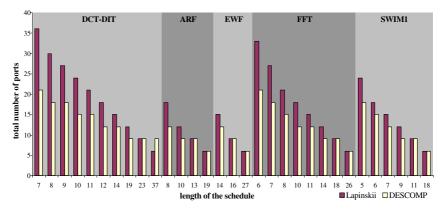

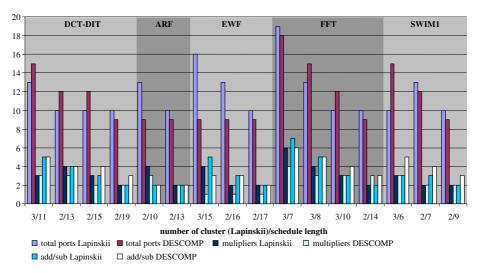

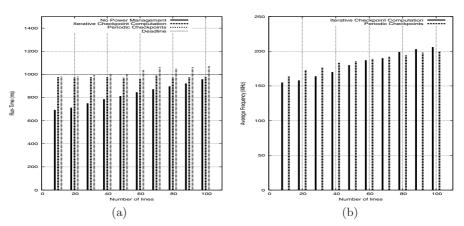

The relative energy consumptions of the three different processor models using the energy management techniques pipeline gating (PG), Pillai software energy management (Pillai) and hardware-based EDF energy management (EDF) are compared as function of the real processor utilization using the processor models similar to the Crusoe respectively the XScale technology. Figure 4 and 5 show the results of the EQUAL benchmark and figure 6 and 7 mirror the relative

Fig. 3. Thread activation and execution during the EQUAL benchmark.

|          | Period | WCET  | Utilization |

|----------|--------|-------|-------------|

| Thread 1 |        | 11655 | 11.6        |

| Thread 2 | 20000  | 7900  | 39.5        |

| Thread 3 | 55000  | 6160  | 11.2        |

| Thread 4 | 25000  | 9425  | 37.7        |

Table 2. Periods and WCETs of the DIFF benchmark.

energy consumption of the *DIFF* benchmark. The figures do not show the total energy consumption of the whole benchmark but rather snap-shots of energy consumption at the appropriate utilization level.

Three curves are shown in all four figures. The one starting slightly above 40% and reaching 73% represents the energy consumption of a processor core supporting only pipeline gating. Because of the assumed energy consumption of 40% in gated mode the minimum energy consumption is likewise 40%. Due to latency bridging, the maximum energy consumption is less than 100% of the energy consumption, i.e. in the case of 100% processor utilization, there are still unused clock cycles left for pipeline gating. This phenomenon can be observed in all measurements.

The second curve, mostly in the middle describes the energy consumption of the benchmarks using a software-based energy management similar to the Pillai technique. The relative energy consumption using the EQUAL benchmark behaves as expected. In the case of the DIFF benchmark the energy consumption using the Pillai energy management exceeds the energy consumption of pipeline gating. This behavior can be explained by the software overhead of the energy management and the readjustment of frequency and voltage only at each thread activation and suspend. Because of the disadvantageous distribution of the threads in the DIFF benchmark, this phenomenon appears only here.

The lowest curve in each figure shows the relative energy consumption resulting from the hardware-based EDF energy management. The EQUAL benchmark is a very uniform benchmark which leads to the approximately proportional energy consumption in figure 4. In contrast to EQUAL, DIFF is a very inhomo-

Fig. 4. Relative energy consumption of the EQUAL benchmark (Crusoe-style).

Fig. 5. Relative energy consumption of the EQUAL benchmark (XScale-style).

geneous benchmark, which leads to a more or less advantageous arrangement of active threads. The low point at about 90% processor utilization using the Crusoe-style model is a result of an advantageous thread arrangement. The flattening of the energy curve at growing processor utilization can be explained by the increasing overlapped thread execution, i.e. with the growing number of usable latency cycles.

Fig. 6. Relative energy consumption of the DIFF benchmark (Crusoe-style).

Fig. 7. Relative energy consumption of the DIFF benchmark (XScale-style).

Realistic Benchmark: For the realistic benchmark, the Komodo microcontroller prototype was built into an autonomous guided vehicle (AGV). Four hard real-time threads control the movements of the vehicle and are used for evaluation. The microcontroller's inputs are the data sent by a line camera, its outputs are pulse width modulated signals (PWM) for two driving engines. The task of the vehicle is to track a steering line on the floor. The four threads perform the following tasks:

- 1. Receiving Camera Data: This thread is responsible for receiving the digital pixel values sent by the line camera. The data is stored in a Java array. The camera thread is activated each time a pixel is received and deactivates itself after writing the received data into the array. After receiving a whole picture, the array is transmitted to the second thread.

- 2. Recognizing the Line: The task of this thread is to recognize the line that guides the vehicle based on the data within the array. This thread is only active during the line detection, otherwise it is deactivated.

- 3. Calculating Steering Data: Together with the data of previous line pictures and the information about the actual positioning of the line, this thread calculates the new driving direction and speed. These two values are forwarded to the next thread.

- 4. Generating PWM Signals: This thread's job is to use the values of direction and speed for calculating PWM signals.

Methodology: Because real current measurements cannot be made using a FPGA prototype and an ASIC is much too expensive, the measurement methodology combines real input data from the AGV prototype with a VHDL simulation of the Komodo microcontroller including the different energy management techniques (pipeline gating, software-based energy management, and hardware-based energy management).

First, the vehicle's control program was executed on the FPGA prototype inside the vehicle. During the first 3.2 million clock cycles a logic analyzer records the signals sent from the line camera. The second step is to use the logged data as input to the simulation running the same vehicle program yielding the frequency and voltage changes and the number of cycles with gated pipeline.

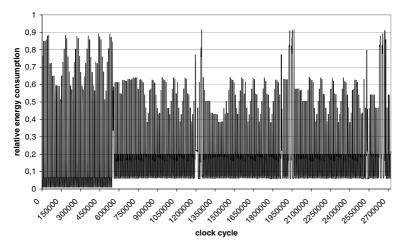

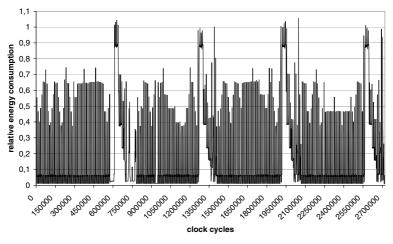

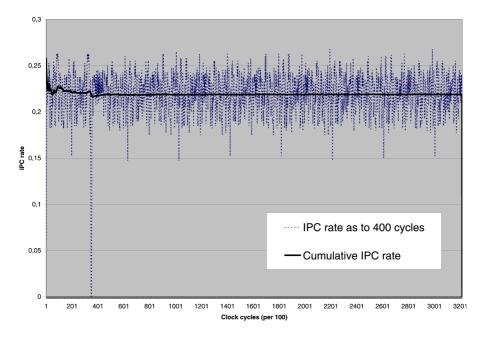

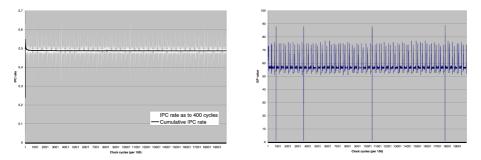

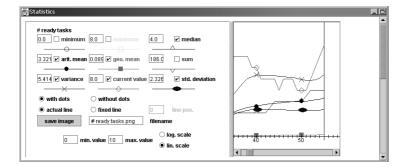

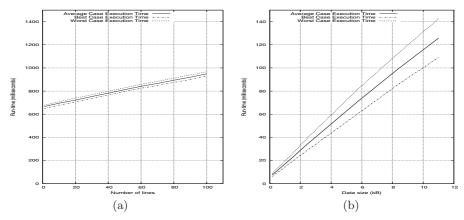

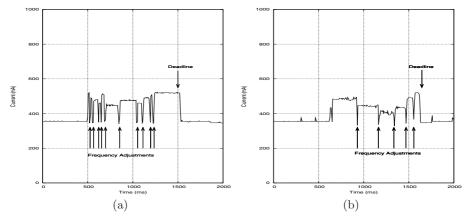

Results: Figures 8-9 present the results of our simulations. The x-axes mirror the time in base clock cycles and the y-axes show the energy consumption relative to a processor without any energy management. The peaks above 1 in figure 9 stem from the assumed overhead of 8% of energy consumption of the base processor because of the added energy management hardware.

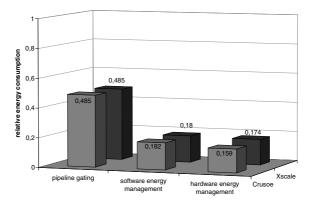

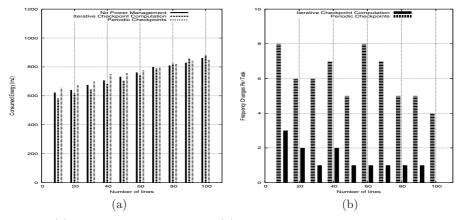

Figure 10 summarizes the simulation results by showing the fractions of energy consumption during the simulated time interval. Each column represents the required energy in the specified technology in comparison to a Komodo microcontroller running at full speed all the time. These values are calculated using the formula in section 1, where C (the capacity of the whole circuit) and f are normalized to 1.

The leftmost bars show the energy consumption using pipeline gating and the highest voltage of the corresponding technology. The reason for the large energy saving of about 51.5% is the low overall processor utilization with an average of 22.6% over the whole time interval. Because we assumed that the energy needed in gated mode is still 40% of the energy in running mode, the required fraction of energy (48.5%) is higher than the overall utilization.

The bars in the middle of figure 10 mirror the results using a software-based energy management similar to the one presented by Pillai et al. within a single threaded processor core. It reaches energy savings of up to 82%.

Fig. 8. Energy consumption using pipeline gating and software based energy management (Crusoe-style model).

Fig. 9. Energy consumption using hardware based EDF energy management (Crusoestyle model).

The remaining bars show the results using the hardware-based frequency/voltage adjustment and pipeline gating. This combination reaches the best results with the least energy consumption due to the fast frequency and voltage switches, the usage of latencies and the fact, that the processor is not idle during voltage/frequency switching. Because of more available voltage levels and a lower voltage at the slow clock rates, the Crusoe-derived version outperforms the XS-cale version.

Fig. 10. Total energy consumption of the AGV benchmark normalized to a Komodo microcontroller running at full speed.

#### 6 Conclusions

This paper presents a new management technique for reducing energy consumption within multithreaded real-time systems. Frequency adjustment and dynamic voltage scaling are managed exclusively by hardware. The management technique is based on the Earliest Deadline First (EDF) scheduling scheme implemented in the multithreaded Komodo microcontroller which is used for benchmarking.

One advantage of hardware-controlled energy management over software-based solutions is the ability of using extremely short periods of underutilization for reducing energy consumption, where software-based solutions are not able to react fast enough. The second advantage is the ability to slow down real-time thread execution at any time during thread execution. Thus, our technique is able to compensate the disadvantage of discrete frequency levels. As third advantage, it should be mentioned that our hardware-based energy management is suitable for both, periodic and sporadic real-time threads. Especially in ubiquitous systems, energy management for aperiodic real-time threads is important.

Our evaluations show that energy consumption could be reduceded to  $\frac{2}{3}$  of an comparable software-based solution. The consumed energy never exceeds the amount consumed by the software-based algorithm. Additionally, the software-based algorithm supports only periodic threads.

#### References

- Kreuzinger, J., Schulz, A., Pfeffer, M., Ungerer, T., Brinkschulte, U., Krakowski, C.: Real-time Scheduling on Multithreaded Processors. In: 7th International Conference on Real-Time Computing Systems and Applications (RTCSA 2000), Cheju Island, South Korea. (2000) 155–159

- Kreuzinger, J., Brinkschulte, U., Pfeffer, M., Uhrig, S., Ungerer, T.: Real-time Event-handling and Scheduling on a Multithreaded Java Microcontroller. Microprocessors and Microsystems 27 (2003) 19–31

- 3. Intel Corporation: Intel PXA26x Processor Family Developer's Manual. (2002)

- 4. Transmeta Corporation: Crusoe TM5500/TM5800 System Design Guide. (2002)

- 5. Texas Instruments: MSP430x43x, MSP430x44x Mixed Signal Microcontroller. (2004)

- Li, H., Bhunia, S., Chen, Y., Vijaykumar, T.N., Roy, K.: Deterministic clock gating to reduce microprocessor power. In: International Symposium on High-Performance Computer Architecture (HPCA). (2003) 113–122

- 7. Shin, D., Kim, J., Lee, S.: Intra-task voltage scheduling for low-energy hard real-time applications. IEEE Design and Test of Computers 18 (2001)

- 8. Pillai, P., Shin, K.G.: Real-time dynamic voltage scaling for low-power embedded operating systems. In: ACM Symposium on Operating Systems Principles. (2001) 89–102

- Jejurikar, R., Gupta, R.: Energy aware task scheduling with task synchronization for embedded real time systems. In: International Conference on Compilers, Architectures and Synthesis for Embedded Systems, Grenoble, France. (2002) 164–169

- 10. Pouwelse, J., Langendoen, K., Sips, H.: Energy priority scheduling for variable voltage processors. In: Int. Symposium on Low Power Electronics and Design (ISLPED), Huntington Beach, CA, USA. (2001)

- Pouwelse, J., Langendoen, K., Sips, H.: Dynamic voltage scaling on a low-power microprocessor. In: 7th ACM International Conference on Mobile Computing and Networking (Mobicom), Rome, Italy. (2001) 251–259

- 12. Krishna, C., Lee, Y.H.: Voltage-Clock-Scaling Adaptive Scheduling Techniques for Low Power in Hard Real-Time Systems. In: Proceedings of Real-Time Applications Symposium. (2000)

- 13. Krishna, C., Lee, Y.H.: Voltage-Clock-Scaling Adaptive Scheduling Techniques for Low Power in Hard Real-Time Systems. IEEE Transactions on Computers **52** (2003)

- Aydin, H., Melhem, R., Mosse, D., Mejia-Alvarez, P.: Power-Aware Scheduling for Periodic Real-Time Tasks. IEEE Transactions on Computers 53 (2004) 584–600

- Brooks, D., Bose, P., Schuster, S., Jacobson, H., Kudva, P., Buyuktosunoglu, A., Wellman, J.D., Zyuban, V., Gupta, M., Cook, P.: Power-aware Microarchitecture: Designing and Modeling Challenges for Next-generation Microprocessors. 20 (2000) 26–44

- Seng, J., Tullsen, D., Cai, G.: Power-sensitive multithreaded architecture. In: 2000 IEEE International Conference on Computer Design: VLSI in Computers and Processors, Austin, TX, USA. (2000) 199–206

- Uhrig, S., Ungerer, T.: Fine-grained power management for multithreaded processor cores. In: ACM Symposium on Applied Computing (SAC 2004), Nicosia, Cypres. (2004)

- Uhrig, S., Ungerer, T.: Fine-grained power management for real-time embedded processors. In: RTS Embedded Systems, Paris, France. (2004) 129–146

- 19. Ernst, R., Ye, W.: Embedded Program Timing Analysis Based on Path Clustering and Architecture Classification. (In: International Conference on Computer-Aided Design (ICCAD '97)) 598–604

- Uhrig, S., Liemke, C., Pfeffer, M., Becker, J., Brinkschulte, U., Ungerer, T.: Implementing Real-time Scheduling Within a Multithreaded Java Microcontroller. In: 6th Workshop on Multithreaded Execution, Architecture and Compilation (MTEAC-6) in conjunction with 35th International Symposium on Microarchitecture (MICRO-35), Istanbul, Turkey. (2002) 57–64

# Reducing System Level Power Consumption for Mobile and Embedded Platforms

Ripal Nathuji and Karsten Schwan

College of Computing, Georgia Institute of Technology, Atlanta, GA 30332 {rnathuji,schwan}@cc.gatech.edu

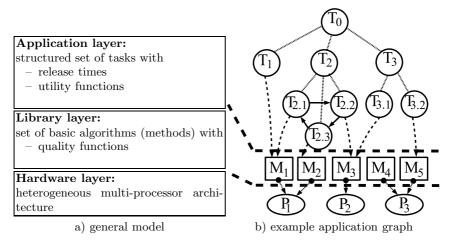

Abstract. The power consumption of peripheral devices is a significant portion of the overall energy usage of a mobile platform. To take advantage of idle times, most devices offer the ability to transition into low power states. However, the amount of energy saved by utilizing these sleep states depends on the lengths and number of idle periods experienced by the device. This paper describes a new process scheduling algorithm which accumulates device usage information in the form of device windows to make power a first class resource: it attempts to increase the burstiness of both device accesses and idle periods, and it provides enhanced behavior for timeout-based sleep mechanisms. An initial implementation based on the default Linux scheduler demonstrates the algorithm's and approach's ability to reduce the average power consumption of devices by increasing device sleep times and reducing transition overheads.

#### 1 Introduction

Mobile devices have become a popular platform for both personal and commercial applications. The increased use of these devices has in turn emphasized the demand for maximizing their battery lifetimes, making power efficiency a critical design goal. Indeed, in order to enable these devices for end users, it is often necessary to employ software techniques in addition to hardware optimizations to achieve the battery lifetimes required by end users. As a result, commercial systems now routinely employ power reduction techniques, ranging from dimming displays, to spinning down disk drives, to turning off (or placing into sleep modes) devices during idle times [1, 2].

An issue faced by most current dynamic techniques for reducing energy usage is that they should not lead to reduced productivity in mobile device usage. Stated more precisely, system metrics like job throughput should not be unduly affected by devices operating in sleep or idle modes. In other words, while reductions in energy usage indicate the need for increasing the burstiness of device usage and thereby improving the extents of device idle times, the consequent changes in the ways in which jobs are executed must not substantially reduce user-centric measures of job scheduling like throughput or response time.

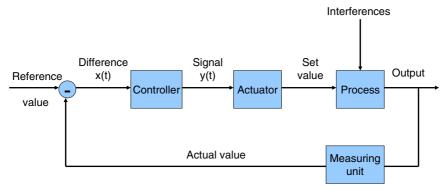

This paper explores a new system-level technique for process scheduling which uses information about a process's device usage to make scheduling decisions. In particular, device usage information is correlated to a process using device windows. The goal of the resulting window-based process scheduler is to utilize this information to schedule processes in a manner which (1) increases the burstiness of device accesses, and (2) increases the durations of idle periods.

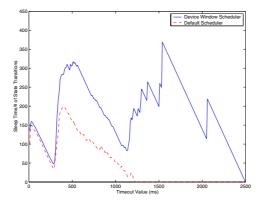

As with related work [3, 4], we assume that the determination of when and how long to put devices to sleep is made at the operating system level, in part because the OS has ready access to the internals of device drivers and performance counters needed to implement effective power measures for power reduction. Consequently, our initial implementation of device window-based scheduling extends the Linux process scheduler on a hardware platform representative of portable devices, using an experimental version of a handheld device that uses Intel's XScale processor. Experimental evaluations of window-based scheduling rely on application scenarios that emulate reasonable device usage patterns. Power measurements use a wireless network device based on the standard 802.11 sleep protocol. These measurements illustrate the ability to save power with this scheduling approach. An analysis of time spent in low power modes and device accesses is also provided. Results indicate improvements of up to 18% in time spent in a low power state and 25% in average power consumption with our wireless 802.11 device.

#### 2 Related Work

There are multiple approaches to the problem of energy reduction in portable devices. Recent processor architectures like Intel's XScale permit dynamic frequency and voltage scaling (DFS/DVS), which can be used to reduce power consumption during program execution [5]. Process schedules can be adjusted to take advantage of these techniques while also meeting application-level requirements like task deadlines [6, 7]. In order to build power-aware hard real-time systems, a design framework that allows for the exploration of power/performance tradeoffs is proposed in [8]. By combining system-level techniques with application-level adaptations, further savings in energy usage can be attained, as shown for multi-media applications [9]. Other methods use compiler-based information to create a compiler/OS collaborative system for frequency scaling [10].

In [11], the authors present an operating system approach that extends the lifetime of a system to some user-specified length by making power a first class resource, and by allocating power strictly to processes. This approach is extended to modified scheduling algorithms in [12]. While increasing device lifetimes, these approaches, however, do not provide any user-level guarantees like throughput or deadlines. In [13], the author utilizes hardware performance counters to perform energy accounting, and proposes energy-aware scheduling techniques based on this accounting.

There has been substantial research on utilizing device idle periods, much of it concerned with communication devices. In [14], the authors propose the use of a separate low power channel to better determine when to turn off the

device. In [1], a modification of the 802.11 protocol at the client and base station is used to collaboratively determine when to put a wireless device to sleep. An adaptive protocol for making device-level sleep decisions is introduced in [15]. The approach is based on the secondary effects of powering down wireless devices on higher layer protocols such as TCP. For greater flexibility, in [16] the authors propose a new application interface for system I/O to provide energy-aware resource usage.

For multiple devices, given a predetermined task schedule and device usage list, [17] describes an algorithm to determine a schedule for device sleep/working states. Given perfect knowledge of tasks' device usage, [18] presents an algorithm that schedules tasks so as to maximize device idle periods. In [19], the authors combine this approach with decisions about when to turn devices on or off using runtime information about per-process device utilization.

Our approach is inspired by the multi-processor scheduling algorithm presented in [20], where the authors utilize processor-cache affinity information to schedule tasks to minimize cache overheads. We develop a power analogue of that approach, the goal being to reduce power consumption by bursting device accesses. The idea is to develop a lightweight dynamic process scheduling algorithm that manipulates inter-device usage characteristics in order to reduce system-level energy consumption. Unlike previous work, we attempt to provide power-enhanced scheduling without any specific information from applications or compilers.

# 3 Motivation and Approach

#### 3.1 Background

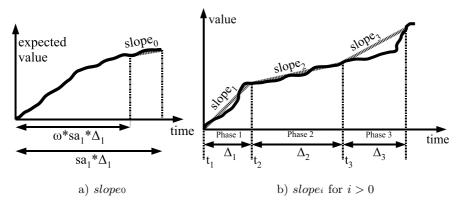

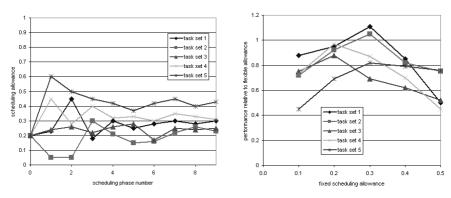

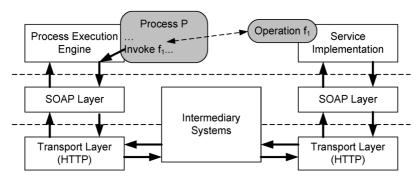

It is well-known that the sizes and distribution of device idle periods can dramatically affect the amount of power that is saved by putting them to sleep. We focus on two particular interactions between idle periods and power saving mechanisms, which are the interactions of idle time distributions with (1) state transition overheads and (2) sleep timeout overheads. Figure 1 illustrates how the distribution of idle periods can affect these attributes. The example depicts a scenario with four periods of device usage. Power state transitions are represented with dotted arrows, and timeout periods with dashed areas. Note that timeout periods overlap with idle periods of the device.

Fig. 1. Bursting Device Accesses.

When the three periods of device usage are coalesced into one larger one, total idle time remains the same, but the device avoids two timeout periods and four state transitions. This results in an increased time spent in sleep state with the same idle time (due to both timeout and state transition overheads). As an example, a wakeup state transition for the 802.11 wireless device can take about  $250\mu s$  during which time the card consumes the amount of power required for the idle state [21], resulting in an energy consumption of approximately .2mJ per wakeup when the card consumes 755mW more power in idle mode than in sleep mode [22]. The energy cost of a timeout period is given by Equation 1, where  $P_{idle}$  is the average power consumed when idle,  $P_{sleep}$  is the sleep power of the device, and  $t_{to}$  is the timeout period. Each timeout that is avoided saves  $E_{to}$ . Using our wireless example again, with a typical timeout value of 10ms,  $E_{to}$  is approximately 7.55mJ. Therefore, by reducing the number of timeouts, and by amortizing the cost of both timeouts and state transitions with longer sleep periods, 'bursting' device accesses can benefit power consumption. For the specific case of wireless network devices, this behavior is also exploited in [22].

$$E_{to} = (P_{idle} - P_{sleep}) * t_{to} \tag{1}$$

The principal goal of our scheduling approach is to manipulate process schedules in order to provide power-efficient inter-device usage times. Given perfect knowledge of device usage requirements for processes, it is possible to determine an optimal schedule for both process execution and the associated schedule for toggling the sleep modes of devices. This paper's approach addresses the more common scenario in which the operating system must schedule processes and manage device states without apriori information about device usage. As a result, we do not require applications to adhere to a specific API to take advantage of device window scheduling, nor do we assume hints or program information provided by compilers. Instead, the idea of process scheduling based on device windows is to dynamically develop information about a process's pattern of device usage based on its past behavior. Past behavior is collected using device windows, which are then used to help schedule processes in order to create suitable inter-device usage times. Stated concisely, (1) device usage information collected at runtime is used to estimate the lengths of device usage patterns, based on which (2) process schedules are changed to better distribute device idle periods (*i.e.*, increased burstiness).

An interesting issue with device idle periods is to make them large enough to enable low power modes but also sufficiently small to avoid device timeouts. This is because systems use timeouts to determine when or whether a device should enter sleep mode. That is, a device enters sleep mode after some pre-determined timeout period and is woken up as soon as it is used by some process. The aggressive approach of using very small timeout values can lead to overall increases in energy usage due to the overheads of frequently toggling device states, and it may also cause additional, wakeup-caused delays for the applications using the device. Conversely, using a conservative timeout value can result in achieving only a fraction of the total possible energy savings. In this context, then, one task of device window scheduling is to create 'good' inter-device usage times.

In order to illustrate the approach, assume that only one device is under consideration and that the scheduler is aware of whether or not a process will use the device the next time it runs. Given this information, the scheduler can 'burst' device access by first scheduling all of the tasks that will use the device and only then running the tasks that will not (or vice versa). Unfortunately, schedulers do not have perfect information about future device usage by processes and must, therefore, use some predictive mechanism. The mechanism advanced in our work assumes that processes begin executing with 'empty' device windows. Whenever a process executes on the CPU, its device window is updated to reflect whether or not the device is used. We next define device windows and their usage in more detail.

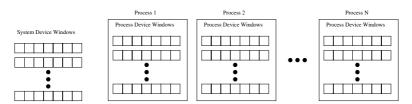

#### 3.2 Device Windows

The role of device windows is to provide information to the scheduler in order for it to determine the next process to be scheduled. There are two kinds of device windows: (1) process device windows and (2) system device windows. Process device windows are used to estimate the likelihood of a process utilizing a device during its next execution period on the CPU. For each device in the system, a unique device window is included in the state of each process. These device windows are updated whenever a process stops executing on the CPU. Specifically, device windows are implemented as statically sized sliding windows. Each time a process is removed from the processor, the window entries are shifted to the right, and the 'last' (leftmost) bit is set if the device was used during the past execution period.

In addition to the device windows allocated to each process, our scheduling algorithm requires some system-wide state. This is realized with *system device windows* that capture system state rather than per-process information. Similar to process device windows, there is a unique system device window for each device. These windows are updated simultaneously with process device windows whenever a process is removed from the processor. Figure 2 illustrates the design of our system with respect to device window state.

Given process and system device windows, the scheduling algorithm determines the most appropriate process to schedule next. When doing so, the scheduler must compare the significance of multiple device windows. This comparison is performed by determining device window "values". The *value* of a device window is a function of its bits. One possible function is to count the number of

Fig. 2. System Device Window Design.

'set' bits in the device window. With larger device windows, however, it may be necessary to not just consider the number of set bits, but also their distribution. For example, consider a device window of [00101] and [11000]. Both have two set bits, but the latter window represents a process that has used the device during its two most recent execution periods. To quantize this difference, device windows can also be compared by the binary values of their bits. In the example, this would result in comparing device window values of 5 and 24. Note that this approach exponentially reduces the significance of a device window bit whenever the window is shifted. Therefore, we define device windows that calculate their values in this manner as 'exponential' device windows. The decision of which type of device window to use is left as a design parameter. In our experiments we utilize exponential device windows for process state, and normal device windows for system state.

An issue is the size of both system and process device windows. With larger windows, the scheduler can accumulate usage data over longer periods of time. The tradeoff, however, is that the information in a longer device window may not accurately represent the current execution characteristics of the process (*i.e.* the data may become stale) for low latency devices. Similarly, small device windows may be too dynamic for higher latency devices. Therefore, device windows should be sized in proportion with the latency of the respective devices to which they are assigned. For system device windows, we utilize a static size of 'one' to allow the scheduler to quickly adapt to changes in device usage patterns of the system.

A final attribute of device windows is the use of window value thresholds. Thresholds are used for both process and system device windows. For process device windows, if the value of the window is greater than the threshold, then the scheduler will predict that the process is likely to use the device the next time it runs on the CPU. We define the *Active Device Set (ADS)* of a process as the set of devices for which the device window value is greater than the threshold. For system device windows, if the window value is greater than the threshold, the scheduler will consider that device as being active in the system. Similar to processes, we define the system *Active Device Set* as the set of devices which are determined to be active in the system. Table 1 lists the various device window parameters discussed in this section.

### 3.3 Device Window Scheduling

The goal of energy-efficient scheduling is to obtain burstiness in device usage. That is, if a device is not currently being used, then preference should be given

| Parameter Definition |                                                                       |  |

|----------------------|-----------------------------------------------------------------------|--|

| size                 | number of bits allocated for a device window                          |  |

| value                | set bit count (normal) or binary value (exponential) of device window |  |

| threshold            | comparison value for a device window                                  |  |

| ADS                  | set of device windows for which value > threshold                     |  |

Table 1. Device Window Parameter Definitions.

| Paramete    | pr Definition                                                           |  |

|-------------|-------------------------------------------------------------------------|--|

| $S_{0,i}$   | 1 if System device window value less than threshold for device $i$ ,    |  |

|             | 0 otherwise                                                             |  |

| $S_{1,i}$   | 1 if System device window value greater than threshold for device $i$ , |  |

|             | 0 otherwise                                                             |  |

| $P_{0,i,p}$ | 1 if Process device window value less than threshold for process $p$    |  |

|             | and device $i$ , 0 otherwise                                            |  |

| $P_{1,i,p}$ | 1 if Process device window value greater than threshold for process $p$ |  |

|             | and device $i$ , 0 otherwise                                            |  |

| $W_{i,p}$   | Process window device value for process $p$ device $i$                  |  |

| $W_{i,max}$ | Maximum window device value for device $i$                              |  |

| $\lambda_i$ | Weight value for device $i$                                             |  |

Table 2. Scheduler Parameter Definitions.

to processes that are not likely to use it. If a device is in use, then processes with high device window values should be preferentially scheduled. We term the previous action as 'idle bursting' (IB) and the latter as 'device bursting' (DB).

As described in Section 3.2, the scheduler utilizes threshold values along with system device windows to determine what devices are active in the system. If a device is active, the scheduler will try to perform device bursting for it, otherwise it will attempt to perform idle bursting. In particular, as described in Table 2, the parameters  $S_{0,i}$  and  $S_{1,i}$  denote whether the scheduler should perform idle or device bursting, respectively, for device i. Given the parameters in the table, we define the maximizing function in Equation 2, where K is the number of devices considered by our scheduler.

$$M(p) = \sum_{i=1}^{K} \lambda_i (S_{1,i} P_{1,i,p} W_{i,p} + S_{0,i} P_{0,i,p} (W_{i,max} - W_{i,p}))$$

(2)

The value returned by Equation 2 depends upon the bursting mode currently occupied by the process system. The  $W_{i,p}$  value for a process is only included in the returned value if the scheduler should perform device bursting for device i. Similarly, the value  $(W_{i,max} - W_{i,p})$  is factored in the value of the maximizing function if the scheduler should perform idle bursting. Given the scheduling parameters and our maximizing function, our simple scheduling algorithm is Algorithm 1. The precise behavior of this process scheduling algorithm depends upon the number of devices under consideration.

# Algorithm 1 Device Window Scheduling Algorithm.

$\forall\ Processes\ i,j \in Runnable$

Choose Process i s.t.  $M(i) \ge M(j) \ (\forall j \ne i)$

Scheduling with a Single Device. Given a single device, the behavior of device window-based scheduling is straightforward. If the scheduler determines that it should perform idle bursting, it will choose the process in the run queue that has the smallest window value, thereby attempting to elongate an existing idle period. Similarly, if device bursting should be performed, the scheduler searches for the process with the largest window value, since a higher window value signifies an increased likelihood that the process will use the device when it is scheduled on the CPU.

Scheduling with Multiple Devices. When the scheduler must consider multiple devices, its behavior is best described using the idea of Active Device Sets (ADS). In particular, the algorithm will give highest preference to processes whose Active Device Sets match the system ADS. If no such processes exist, preference is given to processes whose device sets intersect as much as possible with the system ADS. Note that the scheduler gives least preference to processes that have device sets disjoint from the system ADS.

**Device Weight Values.** The notion of device weights is included in the maximizing function in order to allow the scheduler to give preference to scheduling for particular devices. Specifically, these weights can be used to give preference to creating idle periods for high latency devices with larger timeout values and larger state transition overheads. The motivation is that it is often beneficial, in terms of system power, to increase the number of state transitions for a low latency device in order to allow a device with higher overheads to remain idle.

# 4 Scheduler Implementation

#### 4.1 Linux Scheduler Modification

Our initial implementation of device window scheduling is based upon the epoch-based Linux scheduler. The default Linux scheduler picks a runnable process which has the maximum value returned from the goodness() function. This function will return zero if the process has zero time quantum remaining. If all processes are out of time quanta, the scheduler reassigns quanta to initiate another epoch.

We utilize the *goodness*() function to implement device window-based scheduling. In particular, if a process is both runnable and has a non-zero quantum value in the current epoch, we add the value returned by our maximizing function in Equation 2 to the goodness value. Therefore, we do not modify the usual behavior of the Linux scheduler in terms of epochs and assigned quantum values. Instead, we attempt to provide improved device access behavior by reordering process execution in a given epoch.

#### 4.2 Performance Considerations

Given the scheduling algorithm described in Section 3.3, the scheduler can starve certain user tasks by continually scheduling processes that are either I/O- or

CPU-bound. This can result in poor performance with respect to application-level requirements like response time or other soft real-time guarantees. Our implementation of device window process scheduling prevents such behavior by taking advantage of time epochs in the Linux scheduler. Specifically, tasks cannot experience starvation because our scheduling algorithm will not extend a process's time quantum to increase the length of an idle or busy period for a device. Instead, we attempt to make device usage/idle periods as bursty as possible within the constraint of the epochs. This ensures that applications do not experience any less service than they would with the normal Linux scheduler.

# 5 Experimental Evaluation

#### 5.1 Sitsang Evaluation Platform

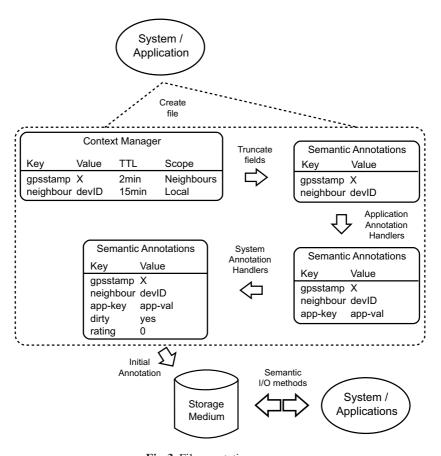

Device window scheduling is experimentally evaluated on XScale-based platforms using Intel's Sitsang evaluation board. This evaluation board is based upon the Intel PXA255 processor. The PXA255 processor integrates the Intel XScale microarchitecture with various controllers and peripherals including a memory controller, universal serial bus support and DMA controller. The evaluation board offers additional features, including a CompactFlash slot, infrared receiver, and a slot for Secure Digital memory cards. The operating system used with the evaluation platform is a patched version of the Linux 2.4.19 kernel.